### Introduction of Direct Sampling Mixer with Low Noise Design

Tokyo institute of technology Araki-Sakaguchi Laboratory Takafumi NASU

### Contents

- Background

- Role of Mixer

- Classification of Mixer

- Introduction of Direct Sampling Mixer (DSM)

- Issues and Objectives

- Noise analysis of SCF networks

- Noise Figure (NF) of DSM

- Conclusion

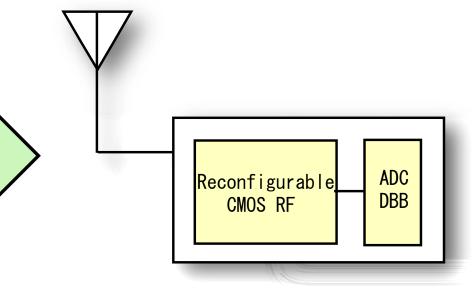

# Background 1

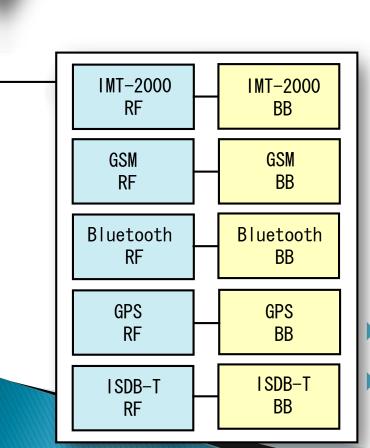

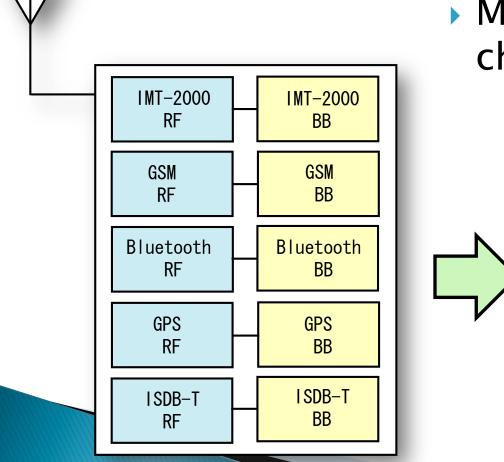

Example of receiver block in mobile terminal

Receiver circuit is being designed for each standards.

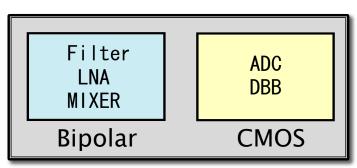

Receiver compose of different process.

SiP(System in Package)

big size high power consumption

### Background 1

Example of receiver block in mobile terminal

#### Multi-standard CMOS 1 chip receiver is desired.

- Requirements ' in wireless cc

- Small s<sup>;</sup>

- Low p

#### **receive**<sup>\*</sup>

### What is Mixer?

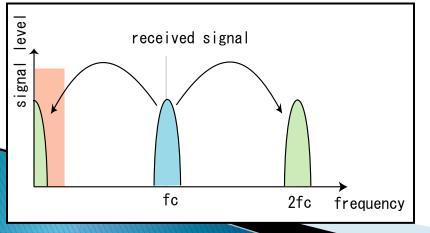

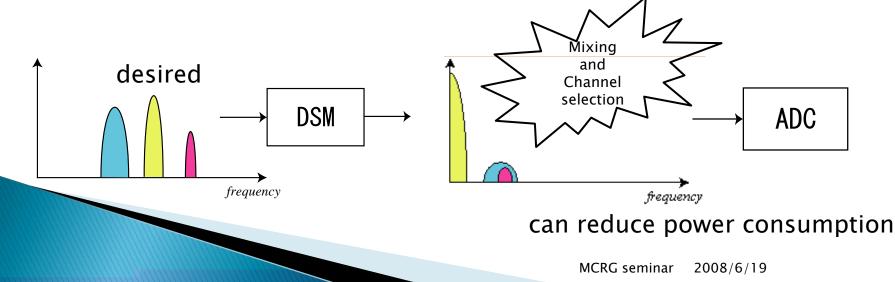

- In receiver, signal received at antenna is handed to ADC.

- In digital stage, transmitted information is demodulated.

- Information data is very low rate compared with carrier frequency.

- To reduce the operation rate of ADC, it is necessary to pick out only information from received signal. It is performed by mixer and filter.

- Where is signal output?

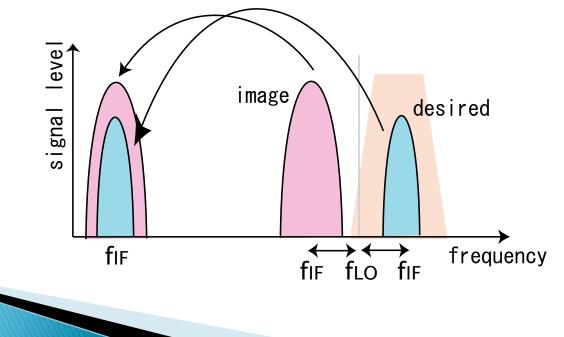

- Intermediate Frequency (super heterodyne)

- good performance

- need image rejection in front of mixer

- Where is signal output?

- Intermediate Frequency (super heterodyne)

- Base Band (Direct-conversion)

- not so good performance (DC offset, flicker noise)

- no image

> suitable for multi-standard receiver

- ✓ How is down-conversion performed?

- Continuous time (Gilbert cell)

- VDD can not be reduced.

- Not suitable for CMOS technology

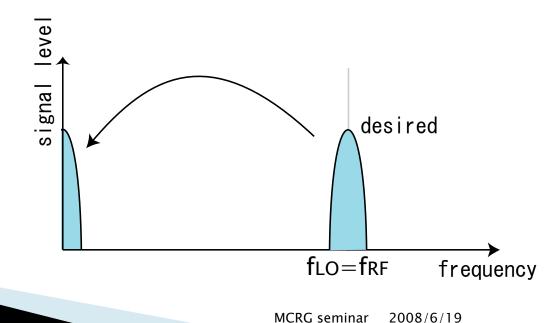

- ✓ How is down-conversion performed?

- Continuous time (Gilbert cell)

- Discrete time (Sampling mixer)

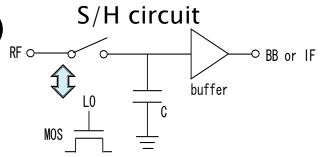

- Sub sampling

- MOS performs as a switch.

- fLO=fRF/n (n: integer)

- Fast switching operation is not needed.

- Holding noise is big issue.

- How is down-conversion performed?

- Continuous time (Gilbert cell)

- Discrete time (Sampling mixer)

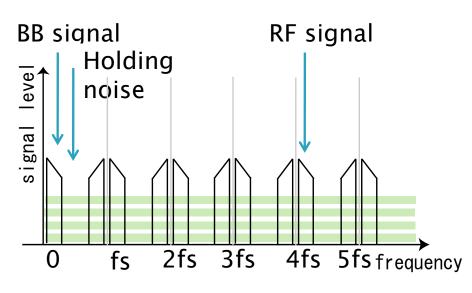

- RF sampling

- flo=frf

- CMOS in deep submicron technology can adapt to fast switching operation.

- Holding noise can be reduced.

11

- Direct Sampling Mixer (DSM)

- Where?

- Direct–conversion

- How?

- RF sampling

Suitable for multi-standard CMOS receiver

DSM is Filter embedded mixer

### <u>A Currente giesticen Som ginne</u>

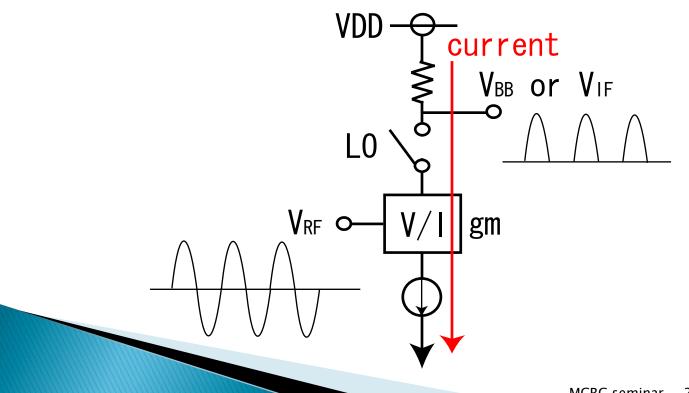

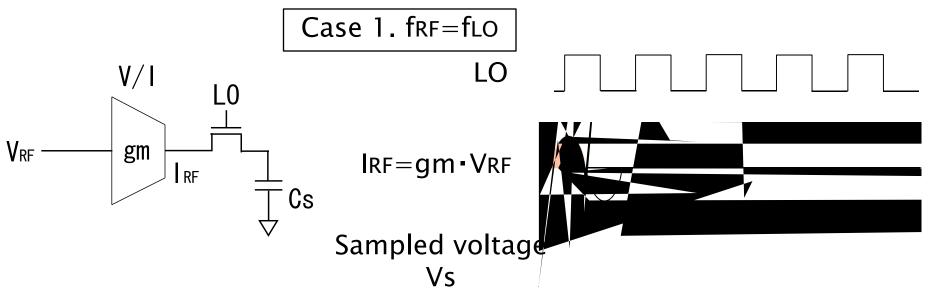

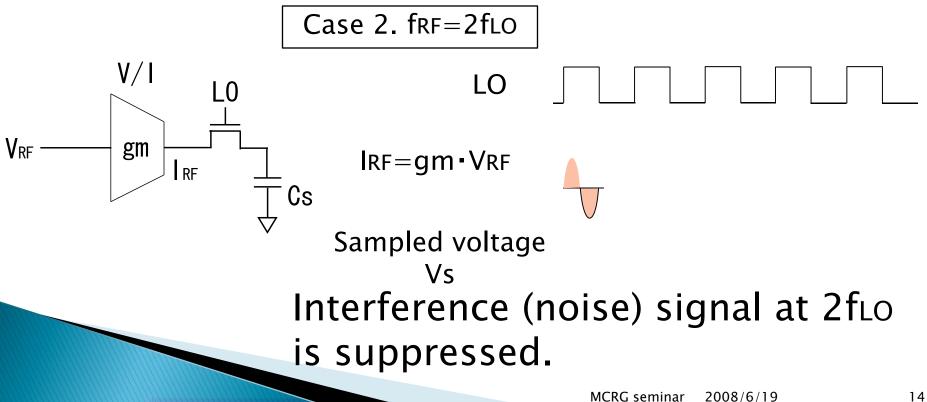

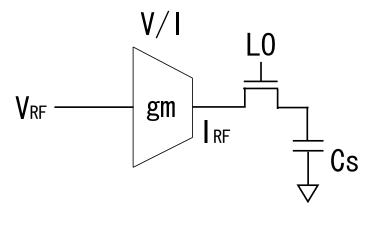

- Input voltage is converted to current by transconductans amplifier.

- Cs integrates current.

- Integration window is controlled by clock LO.

### Desired RF signal is converted to DC.

### <u> Alterizerization Sonic</u>

- Input voltage is converted to current by transconductans amplifier.

- Cs integrates current.

- Integration window is controlled by clock LO.

<u> Autonie staatstigan Somelinne</u>

$$C_{S}V_{S} = \int_{0}^{\frac{T_{LO}}{2}} g_{m}V_{in}e^{j\omega t}dt$$

$$= \frac{g_{m}}{\pi f} \cdot e^{j\omega \left(\frac{T_{LO}}{4}\right)} \cdot \sin\left(\frac{\pi fT_{LO}}{2}\right) \cdot V_{in}$$

$$\left|H_{CI}\right| = \left|\frac{V_{S}}{V_{in}}\right| = \frac{g_{m}T_{LO}}{2C_{S}} \cdot \left|\operatorname{sinc}\left(\frac{\pi fT_{LO}}{2}\right)\right|$$

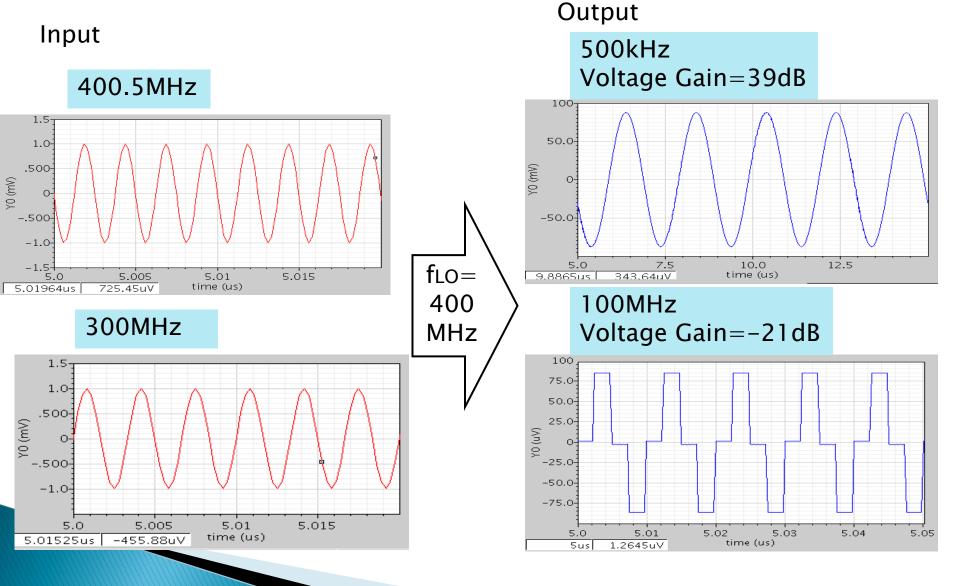

←flo=400MHz

CIS performs as sinc filter. Interferences and holding noise from even frequency can be suppressed.

However, Output rate (= fRF) is too fast.

For ADC, decimation is needed.

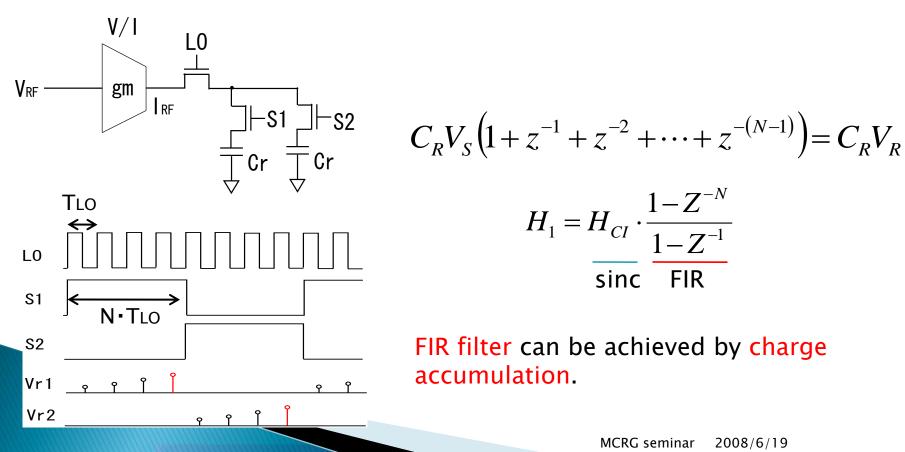

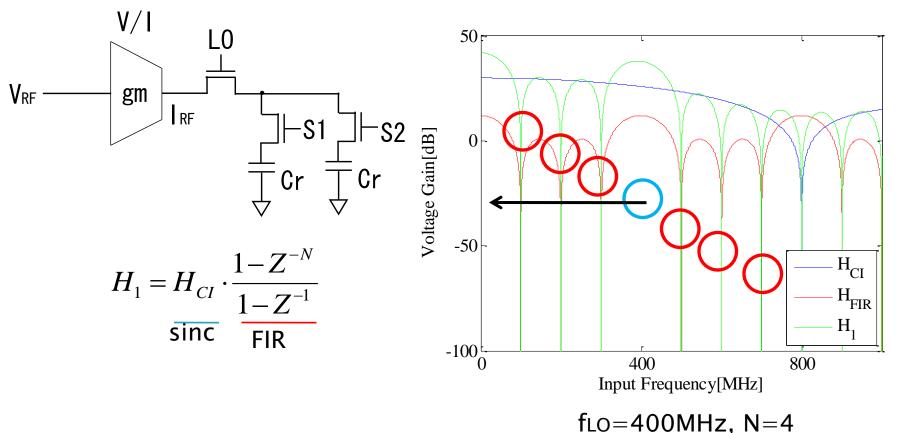

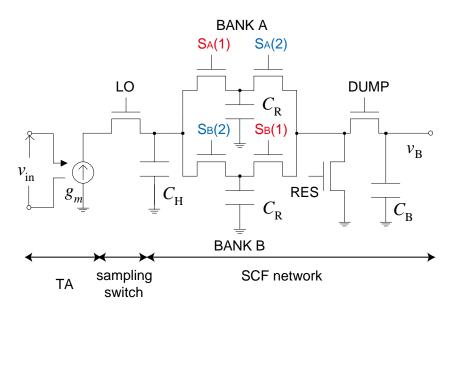

### **Decimation (FIR)**

- Use two rotating capacitor CR

- Accumulate the charge N times

- Output rate = frf(=flo)/N

### **Decimation (FIR)**

Charge accumulation performs as not only decimation, but also FIR (anti- aliasing) filter.

However, filter characteristics is not enough for channel selection.

MCRG seminar 2008/6/19

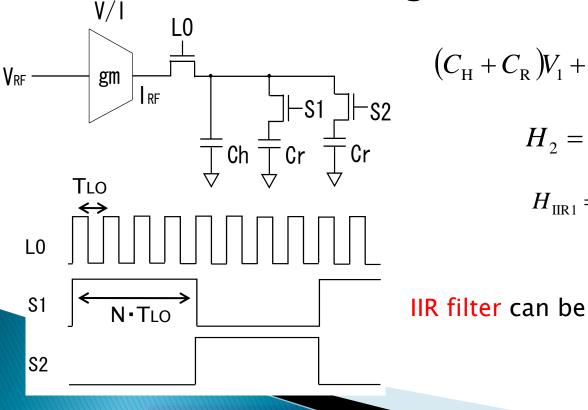

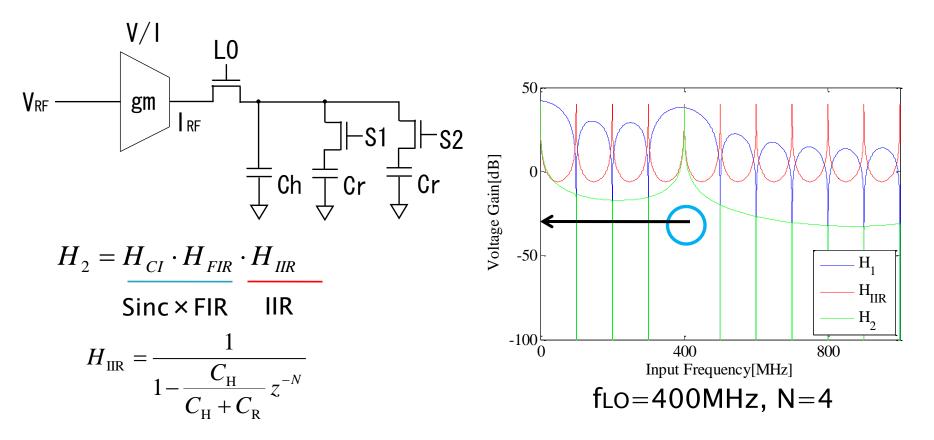

# Charge sharing (IIR)

- Add history capacitor Сн

- In contrast to CR, Cн is not reset.

- At the moment when S1 or S2 become on-state, CH shares the charge with CR.

$$C_{\rm H} + C_{\rm R} V_1 + C_{\rm H} z^{-N} V_{\rm IIR1} = (C_{\rm H} + C_{\rm R}) V_{\rm IIR1}$$

$$H_2 = H_{CI} \cdot H_{FIR} \cdot H_{IIR}$$

$$H_{\rm IIR1} = \frac{1}{1 - \frac{C_{\rm H}}{C_{\rm H} + C_{\rm R}}} z^{-N}$$

IIR filter can be achieved by charge sharing.

# Charge sharing (IIR)

Chanel selection can be achieved by charge sharing IIR filter. Bandwidth is defined by capacitance ratio.

### Architecture-and Feature-of DSM

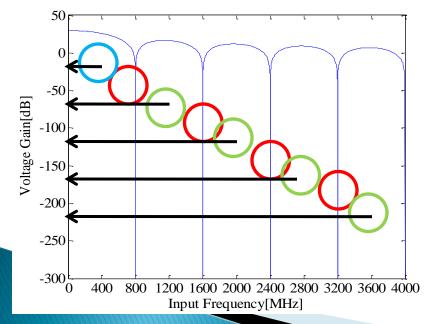

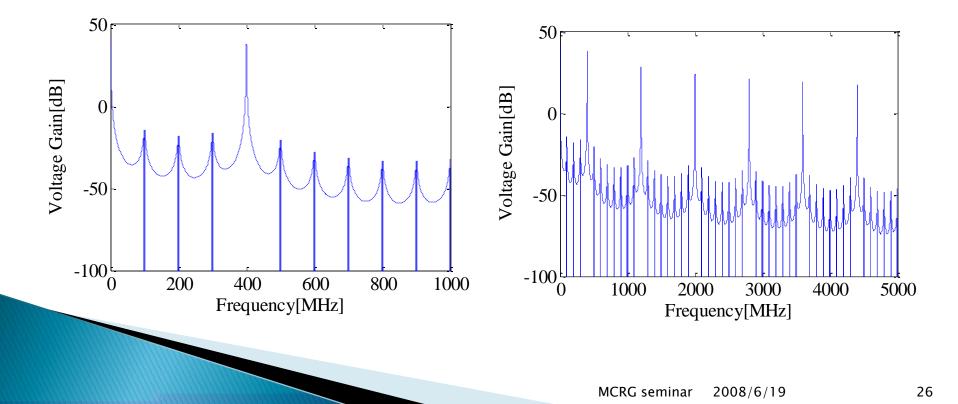

$H_{\rm DSM} = H_{CI} \cdot H_{\rm FIR1} \cdot H_{\rm IIR1} \cdot H_{\rm IIR2}$  $H_{IIR2} = \frac{C_R}{C_R + C_B} \cdot \frac{1}{1 - \frac{C_B}{C_R + C_B}} z^{-N}$ 50 Voltage Gain[dB] 0 -50 -100400 200 600 800 1000 0 Frequency[MHz]

- CMOS performs as a switch.

- Direct Down conversion by charge sampling (no IF)

- Relaxation of the performance requirement of ADC by decimation and filtering

Reconfiguration by changing capacitor set and clock frequency, architecture.

### **Issues and Objectives**

- Noise Figure (NF) of DSM measured from our prototype is over 20dB.

- Gain of CMOS LNA is around 10dB.

- Noise component from DSM can not be negligible.

- Analyzing the noise characteristics of DSM

- Designing the low noise DSM

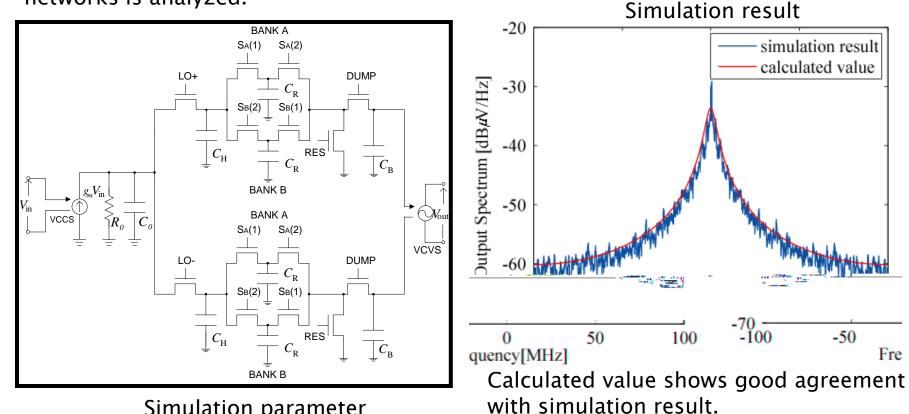

Noise from MOS switches in SCF networks is analyzed.

0.18 µm MOS model from TSMC is used. Switches consist of nMOS.

Simulation parameter

| $f_{LO}$       | $g_m$         | $R_0$  | $C_0$             |

|----------------|---------------|--------|-------------------|

|                | <u>10-z</u> e | 41=O3; | 13:? <b>-</b> EAS |

|                | on esní i s   | iAs Z  |                   |

| pi 0.25i - 2pi |               |        | 20                |

components from TA is dominant.

The noise level is in inverse proportion

to capacitance value.

In practical parameter, noise

Fre

### Noise Figure (NF) of DSM

Assuming that noise from TA is dominant,

$F_{DSM}(f) = \frac{SNR_{in}(f+f_{LO})}{SNR_{out}(f)} = \frac{N_{out}(f)}{G(f+f_{LO})N_{in}(f+f_{LO})} \qquad N_{TA} : \text{internal noise from TA}$

$$\cong 1 + \frac{N_{TA}(f + f_{LO})}{GN_{in}(f + f_{LO})} = 1 + F_{TA}(f + f_{LO})$$

$F_{TA}$  : internal noise from T  $F_{TA}$ : noise factor of TA

Including buffer circuit which is located in next stage,

In prototype which was made in 2006, noise characteristics deterioration is caused by gain degradation.

### Conclusion

- DSM can realize a reconfigurable RF circuit, and is suitable for CMOS technology.

- However, some issues are remained.

noise characteristics, nonlinearity,

variety of filtering characteristics ...

- To achieve low NF, it is necessary to improve the gain of DSM.

# Appendix

### **Frequency Characteristics**

$f_{LO}=400MHz$ , N=4 CH=20pF, CR=0.2pF, CB=2pF

### Filter embedded Mixer